TECHNICAL ARTICLES

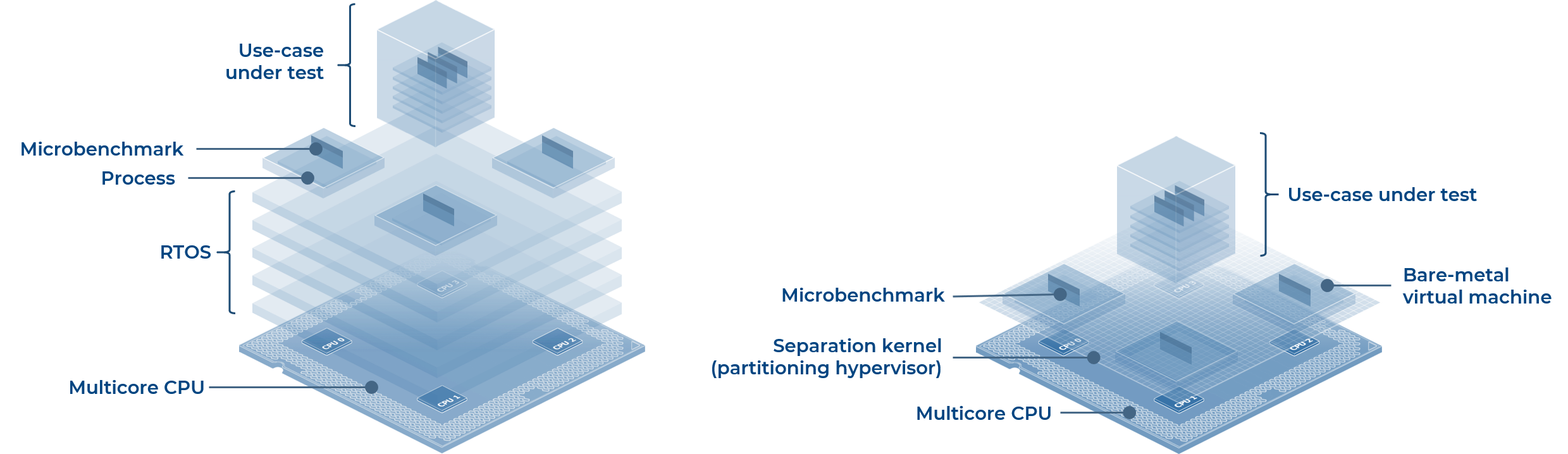

CAST-32A

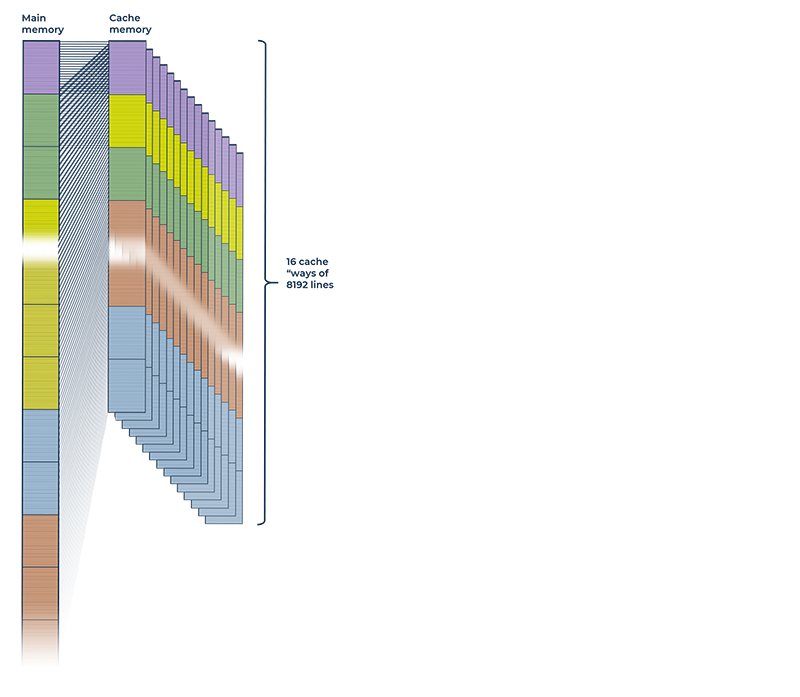

What is Cache Coloring and How Does it Work?

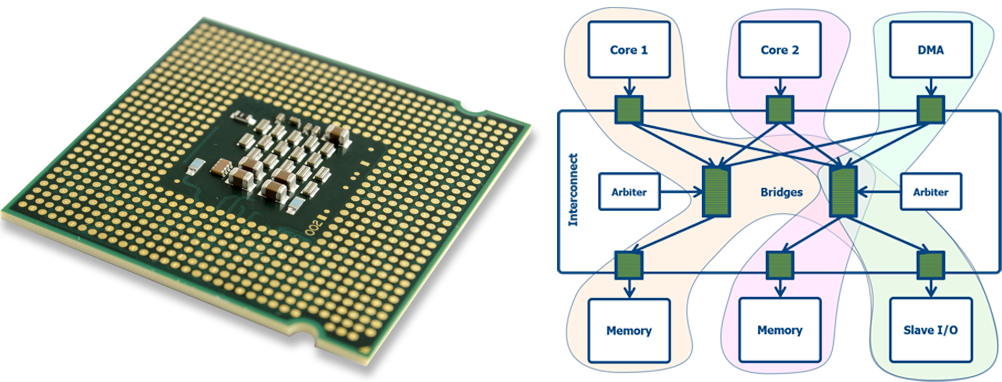

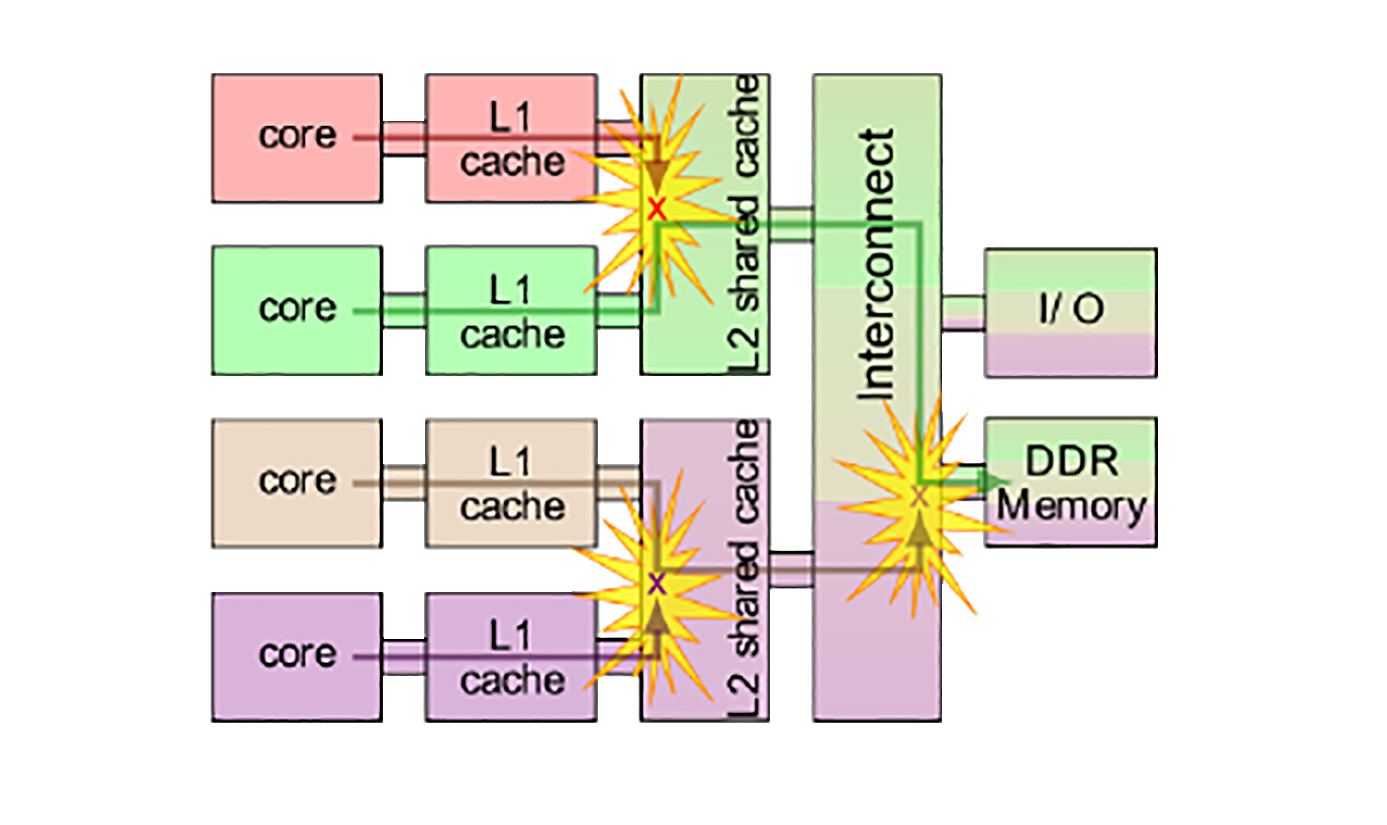

Challenges Building Safe Multicore Systems

Field Notes: Safety-Critical Systems Symposium 2020

TC-16/51: Adding Bottom Up Interference Analysis for MCPs